email: kpapadimitriou

Chania, Crete, 73100, Greece

office: Sciences' buidling, 137.B.69

|

|

Quick-view profile

email: kpapadimitriou Chania, Crete, 73100, Greece office: Sciences' buidling, 137.B.69 |

|

| Research Interests |

| Education |

| Selected Publications |

| Research and Industry Experience |

|

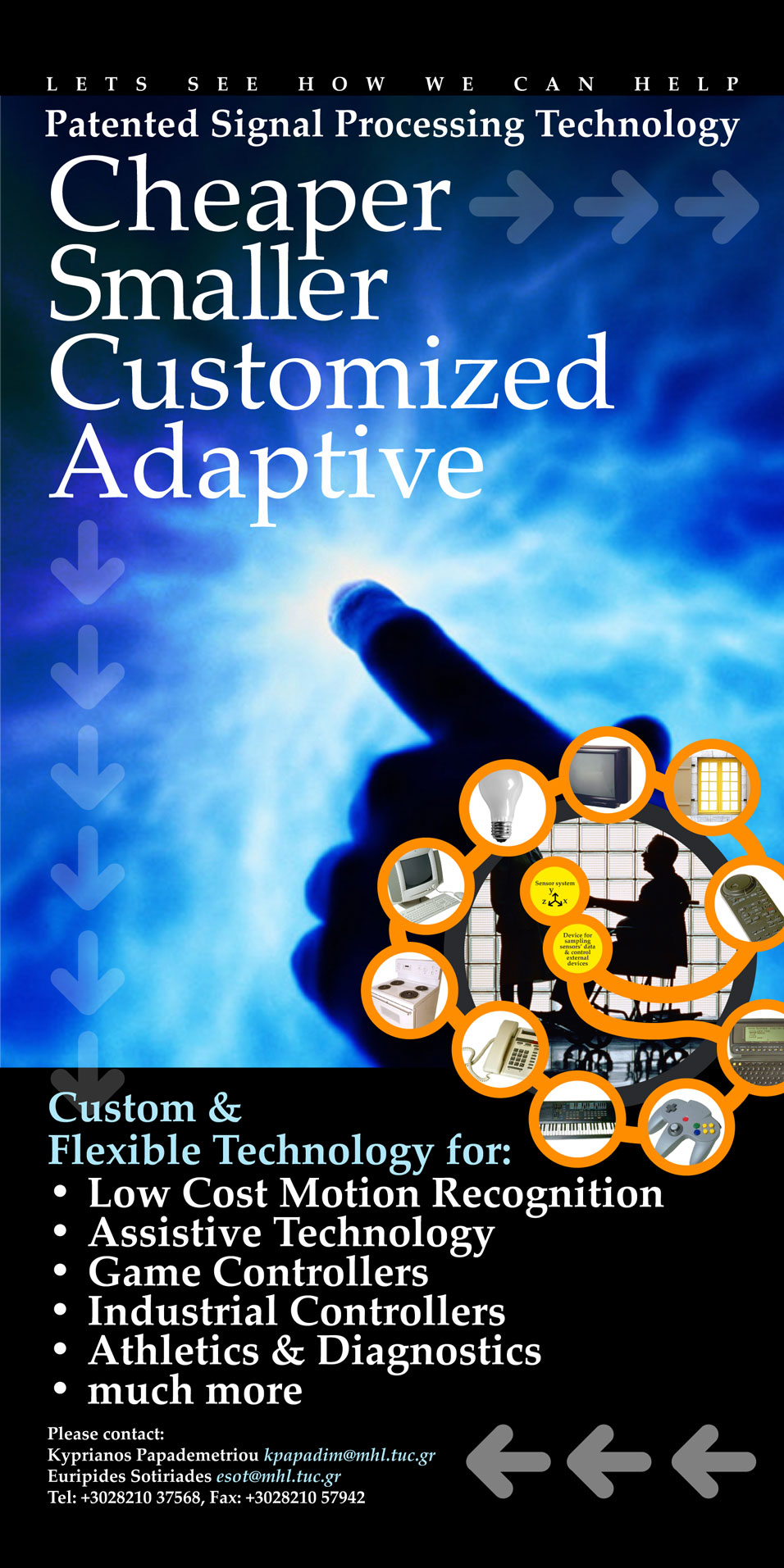

Predoctoral scholar Studied domains that can benefit from partial reconfiguration technology; studied commercial reconfigurable coarse-grained architectures Principal investigator for the commercialization of a research result through spin-off In-more-Tech

|

|

| Publications |

Publications that appear in IEEE Conferences or Journals are subject to the ©IEEE Copyright policies. Publications that appear in ACM Conferences or Journals are subject to the ©ACM Copyright policies. IEEE and ACM own the copyright to all material published by the IEEE and ACM respectively. Personal use of this material is permitted.

| Teaching Experience |

| Distinctions and Awards |

| Service to the Profession |

| Additional Information |